## École Polytechnique Fédérale de Lausanne

On the Enforcement of Attestable Availability Guarantees for Arm-based Industrial Multi-Tenant Real-Time Systems

by Edouard Michelin

### **Master Thesis**

Approved by the Examining Committee:

Prof. George Candea Thesis Advisor

Dr. Christian Göttel, Dr. David Kozhaya Thesis Supervisors

> EPFL IC IINFCOM DSLAB INN 330 (Bâtiment INN) Station 14 CH-1015 Lausanne

ABB Corporate Research Center Industrial Software Systems Segelhofstrasse 1K CH-5405 Baden-Dättwil

August 29, 2025

|                                             | The ultimate inspiration is the deadline. — Nolan Bushnell |

|---------------------------------------------|------------------------------------------------------------|

|                                             |                                                            |

| Dedicated to my parents, Christophe and Mar | yline, and to my brother, Charles.                         |

|                                             |                                                            |

|                                             |                                                            |

|                                             |                                                            |

|                                             |                                                            |

# Acknowledgments

I would like to begin by thanking my family for encouraging me to pursue my studies and for supporting me along the way. I would not be where I am today without them.

I am grateful to my supervisors at ABB, Dr. Christian Göttel and Dr. David Kozhaya, for the opportunity to carry out this thesis with them, as well as for their valuable guidance and advice throughout the project.

I also thank my EPFL supervisor, Prof. George Candea, for his support during my research and for the opportunities he has offered me during my studies.

Baden, August 29, 2025

**Edouard Michelin**

## **Abstract**

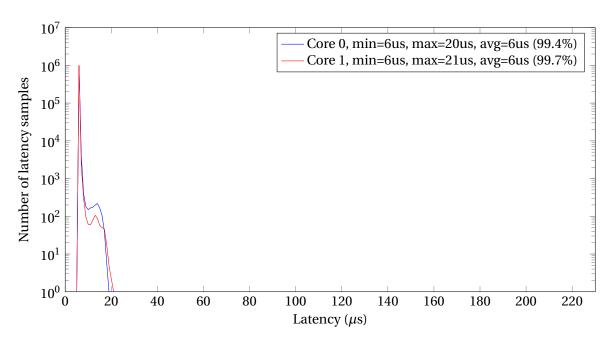

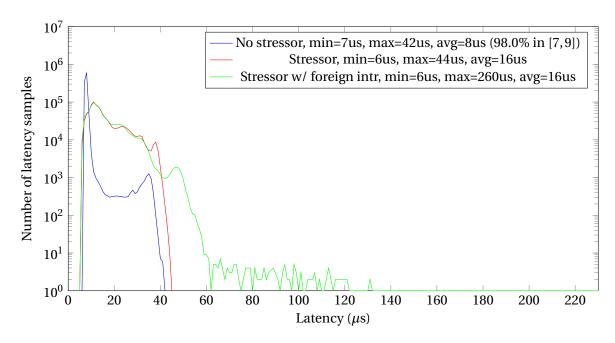

With the rise of Industry 4.0, industries increasingly rely on digital technologies to enable automation, remote control, as well as other real-time services. The integration of sensors, smart devices, and high-speed connectivity is transforming traditional industrial systems into interconnected cyber-physical infrastructures. The convergence of information technology (IT) and operational technology (OT) offers significant operational benefits but also introduces critical security challenges due to fundamental differences between the two domains. OT systems are constrained by strict timing requirements and conservative standards, while IT requires frequent, precise security updates. To remediate the ripples created when bringing these two worlds together, we propose a novel security architecture that bridges remote attestation of execution with guarantees of real-time availability for industrial control systems (ICS). Leveraging commodity Arm TrustZone platforms, our design enforces user-defined policies, and ensures predictable and verifiable operation. We implement a prototype that demonstrates support for high-frequency real-time workloads (period shorter than  $10\mu$ s) with low scheduling latency (as low as  $6\mu$ s), preserving confidentiality and integrity while providing robust attestation, marking a practical path for the secure digital transformation of industrial systems.

### Résumé

Avec l'essor de l'Industrie 4.0, les industries s'appuient de plus en plus sur les technologies numériques afin de permettre l'automatisation, le contrôle à distance ainsi que d'autres services en temps réel. L'intégration de capteurs, d'appareils intelligents et de connexions à haute vitesse transforme les systèmes industriels traditionnels en infrastructures cyber-physiques interconnectées. La convergence des technologies de l'information (IT) et des technologies opérationnelles (OT) offre des avantages opérationnels significatifs, mais introduit également des défis de sécurité critiques en raison des différences fondamentales entre ces deux domaines. Les systèmes OT sont soumis à des contraintes strictes en matière de temps d'exécution et à des normes conservatrices, tandis que les systèmes IT nécessitent des mises à jour de sécurité fréquentes et précises. Afin de remédier aux problèmes générés par cette convergence, nous proposons une nouvelle architecture de sécurité qui associe l'attestation d'exécution à distance à des garanties de disponibilité en temps réel pour des systèmes de contrôle industriel (ICS). En tirant parti des plateformes Arm TrustZone grand public, notre conception applique des politiques définies par l'utilisateur et assure un fonctionnement prévisible et vérifiable. Nous mettons en œuvre un prototype qui démontre la prise en charge de tâches temps réel à haute fréquence (période inférieure à  $10\mu$ s) avec une faible latence de planification (aussi basse que  $6\mu$ s), tout en préservant la confidentialité, l'intégrité et en offrant une attestation robuste, ouvrant ainsi une voie concrète vers une transformation numérique sécurisée des systèmes industriels.

# **Contents**

| Ac | knov  | wledgments                                 | 1  |

|----|-------|--------------------------------------------|----|

| Ał | ostra | ct (English/Français)                      | 2  |

| 1  | Intr  | roduction                                  | 6  |

| 2  | Bac   | ekground                                   | 8  |

|    | 2.1   | Industrial Control Systems                 | 8  |

|    |       | 2.1.1 Real-Time Systems                    | 8  |

|    |       | 2.1.2 Scheduling of Shared Resources       | 10 |

|    |       | 2.1.3 Availability of Resources            | 11 |

|    |       | 2.1.4 Multi-Tenancy                        | 12 |

|    | 2.2   | Trusted Computing on Arm Platforms         | 12 |

|    |       | 2.2.1 Enforcement                          | 14 |

|    |       | 2.2.2 Limitations                          | 15 |

|    | 2.3   | Remote Attestation Model                   | 15 |

|    |       | 2.3.1 Root of Trust                        | 16 |

|    |       | 2.3.2 Device Identifier Composition Engine | 17 |

| 3  | Mot   | tivation and Goals                         | 19 |

|    | 3.1   | Problem Statement                          | 19 |

|    | 3.2   | Threat Model                               | 20 |

|    | 3.3   | Closely Related Work                       | 21 |

| 4  | Des   | sign                                       | 23 |

|    | 4.1   | System Requirements                        | 23 |

|    |       | 4.1.1 Hardware Components                  | 23 |

|    | 4.2   | The Three Powers                           | 24 |

|    |       | 4.2.1 Executive: the Availability Monitor  | 24 |

|    |       | 4.2.2 Legislative: Real-Time Policies      |    |

|    |       | 4.2.3 Judiciary: the Attestation Engine    |    |

| 5  | Imp   | plementation                               | 37 |

| 6  | Eval         | uation                                    | 41 |  |  |

|----|--------------|-------------------------------------------|----|--|--|

|    | 6.1          | Performance Evaluation                    | 41 |  |  |

|    |              | 6.1.1 The Trusted Schedulers in Details   | 42 |  |  |

|    |              | 6.1.2 The Attestation Engine              | 46 |  |  |

|    |              | 6.1.3 The Critical Real-Time Tasks        | 47 |  |  |

|    | 6.2          | Security Evaluation                       | 49 |  |  |

|    |              | 6.2.1 TCB                                 | 49 |  |  |

|    |              | 6.2.2 Security Analysis                   | 49 |  |  |

|    | 6.3          | Case Studies                              | 51 |  |  |

|    |              | 6.3.1 A Sample Industrial Setup           |    |  |  |

|    |              | 6.3.2 End-to-End Remote Attestation       | 52 |  |  |

| 7  | Disc         | ussion                                    | 54 |  |  |

|    | 7.1          | Portability of the Design to Other ISAs   | 54 |  |  |

|    | 7.2          | Limitations                               | 54 |  |  |

|    | 7.3          | Future work                               | 55 |  |  |

| 8  | Rela         | ted Work                                  | 57 |  |  |

| 9  | Con          | clusion                                   | 60 |  |  |

| Bi | Bibliography |                                           |    |  |  |

| A  | Sur          | vey on development boards                 | 70 |  |  |

| В  | Turi         | ning legacy RT tasks into secure RT tasks | 72 |  |  |

## Chapter 1

### Introduction

With the ongoing fourth industrial revolution, industries rely more than ever on digital technologies to drive automation, efficiency, and new services. The integration of sensing capabilities, smart devices, and high-speed connectivity is transforming traditional mechanical industrial systems into cyber-physical ones. This trend, often summarized under the term *Industry 4.0*, promises significant benefits such as predictive maintenance, adaptive production, and real-time monitoring. At the same time, it increases the reliance on interconnected infrastructures and broadens the potential attack surface. The once clear line between Information Technology (IT) and Operational Technology (OT) is becoming increasingly blurred as both domains converge.

While IT has a long tradition of rapidly adopting new security and networking solutions, OT environments tend to be more conservative due to regulatory requirements, standardization, and the high costs associated with downtime or recertification. As a result, OT standards are updated infrequently, and standardization bodies often struggle to reach consensus on specific implementation details, producing broad standards that lack precision. In contrast, IT security must be continuously updated and implemented with precision, as malicious actors will exploit any gaps in the architecture. Historically, OT has been viewed as a constrained environment, with access limited to personnel working in the field, whereas IT spans a much larger scope, resulting in an exponentially larger attack surface. Bringing IT and OT together introduces a wide range of potential vulnerabilities, with numerous intrusion vectors, into a world that, until the advent of Industry 4.0, largely operated in compartmentalized environments with limited focus on security. IT resources, being widely accessible and often open-source, benefit from a large community that helps identify and fix implementation bugs. OT, on the other hand, has relied on specialized equipment and a more closed-source approach, which has historically limited its security capabilities, particularly given the operational constraints and strict timing requirements of industrial control systems.

The convergence of IT and OT, while offering significant operational benefits, also introduces critical vulnerabilities because of the fundamental differences between the two domains. In this

work, we address the ripples created by bridging these two worlds. We propose a security architecture that suits both environments, one that preserves the real-time reliability and deterministic behavior of industrial systems, while also offering new security perspectives to the OT world to defend against modern threats. More specifically, we introduce a hardware-software co-design that provides attestable availability guarantees.

In recent years, research has addressed availability guarantees for industrial applications [4, 51, 85, 86, 89], as well as proof of execution [23, 54, 56, 87]. To the best of our knowledge, we are the first to bridge the gap between these security properties. We build on the widely available Arm TrustZone [15], analyze the requirements for such an architecture, and propose a design that can serve as a blueprint for future industrial environments. To validate our approach, we implement a prototype on a TrustZone-enabled development kit and evaluate its performance to assess both applicability and limitations. Our evaluation shows that the proposed design can be realized on commercially available hardware and applied to representative workloads. The results suggest that our architecture can preserve real-time constraints while offering combined security properties, indicating a viable path for the secure digital transformation of industrial systems.

In summary, we make the following contributions:

- A novel security architecture that bridges attestation of execution with guarantees of real-time availability, even in the presence of a fully compromised normal world OS present from system startup.

- An Availability Monitor that enforces user-defined policies to maintain real-time availability, and an Attestation Engine that produces verifiable evidence of correct scheduling, execution, and configuration.

- Commodity-ready deployment by leveraging resource-efficient Arm multiprocessor platforms, enabling predictable and verifiable trust for critical industrial infrastructures.

- A prototype implementation and evaluation showing that our architecture supports high-frequency real-time execution (up to 110 kHz) with low scheduling latency (as low as 6  $\mu$ s), while preserving confidentiality and integrity of proprietary code and data.

## **Chapter 2**

# **Background**

### 2.1 Industrial Control Systems

Industrial Control Systems (ICS) are at the core of Operational Technology (OT). Their role is to ensure that industrial processes follow their expected behavior. They do so by repeatedly collecting data, received from one or more sensors, performing validation operations, and taking action based on the outcome of the verification. This verification procedure, referred to as control loop or control cycle, is run periodically and is most often mission-critical. Consequently, the control loops in an ICS have high availability requirements, and must react to inputs from their environment before a faulty process can have an impact on subsequent operations. This imposed time limit is referred to as deadline, and the tasks that need to complete in such given time constraints, i.e., before reaching a deadline, are called real-time tasks.

### 2.1.1 Real-Time Systems

A real-time system comprises a set of cores (here sometimes referred to as computational resources), a set of shared resources (which we differentiate from computational resources by referring to them as non-computational resources, devices, or peripherals), and a set of real-time tasks [27]. Contrary to common assumptions, real-time systems impose timing constraints related to a deadline, and need not necessarily be fast or instantaneous. When instances of a task, called jobs, must always complete before reaching their deadline, we say that the timing constraint is hard. Whereas it is said to be soft when the deadline can be missed on some occasion, with low probability, and without having a direct negative impact. In case the tasks of a real-time system have a hard deadline, that system is called a hard real-time system, and we say that the tasks of such a system are critical. Depending on the way they are released (i.e., scheduled), tasks can be periodic, sporadic, or aperiodic. An aperiodic task is scheduled at unpredictable intervals. On the opposite side of the spectrum,

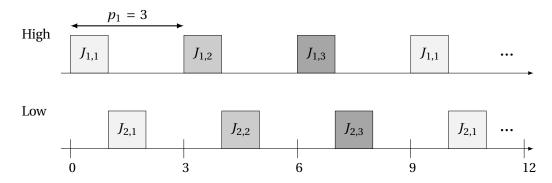

Figure 2.1: Scheduling of two tasks  $T_1 = (3,1,1,\emptyset)$  and  $T_2 = (3,1,1,\emptyset)$  with  $P(T_1) > P(T_2)$ , each of which has three jobs, i.e.,  $J(T_1) = \{J_{1,1}, J_{1,2}, J_{1,3}\}$  and  $J(T_2) = \{J_{2,1}, J_{2,2}, J_{2,3}\}$ .

periodic tasks are scheduled at strict, predefined cycles. Lastly, a sporadic task is an aperiodic task with a deadline. In ICS the focus is on periodic tasks, as control loops are released at regular intervals and must complete before their deadline.

Let  $\mathscr{C} = \{C_i \mid i = [1, n], n \in \mathbb{N}\}\$  be the set of cores of the system,  $\mathscr{T} = \{T_i \mid i = [1, n], n \in \mathbb{N}\}\$  be the set of tasks of the system, and  $\mathcal{R} = \{R_i \mid i = [1, n], n \in \mathbb{N}\}\$  be the set of shared resources available on the system. Formally, we characterize the periodic tasks of a system as a 6-tuple  $(\phi, p, e, D, c, R)$ , where  $\phi$  is the release time of its first job on the system, called its phase, p is its period, that is, the time interval between the release of successive jobs, e is the execution time of the task, often defined as the Worst Case Execution Time (WCET) of all its jobs, D is the minimum relative deadline of its jobs,  $c \in \mathcal{C}$  is the core on which the task will be scheduled and run, and  $R \subset \mathcal{R}$  is the set of resources the task accesses. In order to simplify this definition, for all tasks we say that the phase is defined as the starting time of the system, i.e.,  $\phi = 0$ , and the relative deadline of the jobs is equal to the period, that is, D = p, so that the tasks  $T_i \in \mathcal{T}$  in the system are defined as the 4-tuple  $(p_i, e_i, c_i, R_i)$ . The utilization  $u_i$  of a task  $T_i \in \mathcal{T}$ , given by  $U(T_i) = u_i$ , is computed as  $u_i = e_i/p_i$ , and provides a measure of the proportion of computing resources consumed by the task. We denote  $J(T_i)$  the set of jobs of the task  $T_i \in \mathcal{T}$ . The jobs  $J_{i,j} \in J(T_i)$ ,  $T_i \in \mathcal{T}$ ,  $j \in [1, |J(T_i)|]$  of a task  $T_i \in \mathcal{T}$  are scheduled in order, with the interval of time between two consecutive releases being their period. In other words, all jobs  $J_{i,j}$ , j > 1 of a task  $T_i$  are scheduled and must complete in the time frame  $[(j-1) \cdot p_i, j \cdot p_i]$ with time frame of  $J_{i,1}$  being  $[0, p_i]$ . The order in which the jobs of different tasks are scheduled depends on the priority of their task. Different algorithms are used to compute the priority of tasks, which can either be fixed, or dynamic. Two well-known examples of such algorithms are the fixed priority Rate Monotonic (RM) [49] algorithm, which gives higher priority to tasks with a shorter period, and the dynamic priority Earliest Deadline First (EDF) [21], which, every time the scheduler has to take a scheduling decision, gives precedence to the task closest to its deadline. We denote  $P(T_i)$  the priority assigned to task  $T_i \in \mathcal{T}$ , and illustrate the scheduling of two tasks  $T_1 = (3, 1, 1, \emptyset)$ and  $T_2 = (3, 1, 1, \emptyset)$  with  $P(T_1) > P(T_2)$ , each of which has three jobs, i.e.,  $J(T_1) = \{J_{1,1}, J_{1,2}, J_{1,3}\}$  and  $J(T_2) = \{ J_{2,1}, J_{2,2}, J_{2,3} \}$  in Figure 2.1.

Periodic and aperiodic tasks can coexist on a hard real-time system. In that case, the objective of the task scheduler is that periodic tasks do not miss their deadline, while minimizing the response time of aperiodic tasks. The simplest way to fulfill this mission, when the response time of the aperiodic tasks is not critical, is to treat them as background tasks [47, 88]. In background scheduling, aperiodic tasks are assigned the lowest priority on the system, which as a result do not impact the schedulability of periodic tasks in any way. However, it presents the disadvantage of increasing the response time of aperiodic tasks as the total utilization of the system by critical tasks, denoted  $\mathscr{U} = \sum_{T_i \in \mathscr{T}} U(T_i)$ , increases. There exist more advanced techniques that provide a faster response time to aperiodic, which leverage a periodic server, such as a polling server or a deferrable server [70]. However, the faster response times come at the cost of increased scheduler complexity.

### 2.1.2 Scheduling of Shared Resources

Traditional schedulers, used for instance in consumer personal computer systems, primarily focus on managing the availability of computational resources. Their role is to balance the execution of processes across CPU cores according to some strategy, for which the objectives are often to provide overall system performance, fairness towards all processes, and good user experience. These objectives differ significantly from those of real-time schedulers, making them unsuitable for real-time tasks [74]. Real-time constraints require the scheduling of both computational resources and non-computational resources, such as connected devices (e.g., network card, sensors, actuators, etc.), which need to be obtained by real-time tasks in a deterministic and timely manner, that is, within a strict timing constraint. Should a required sensor or actuator become unavailable and cause a job to miss its deadline, the entire protection function (i.e., control loop) could become worthless, which could have severe consequences in a safety-critical real-time system. An example of such a scenario is the incapacity of a control loop to obtain up-to-date data from a proximity sensor in industrial robotics, where articulated robots [1] can lift heavy payloads, such as car parts. These sensors serve to cut system power when two moving parts come dangerously close, preventing costly collisions.

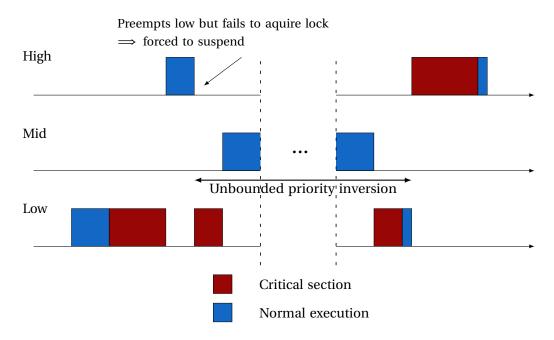

The scheduling of shared devices on a system brings new challenges, potentially creating scheduling problems. Two well-known scheduling problems are deadlocks, and priority inversions, in which a lower priority task holding the lock on a shared resource prevents a higher priority task from acquiring the lock and executing. This issue becomes especially important when tasks that do not use the shared resource, but have a priority higher than the task holding the lock and lower than the blocked task, preempt the execution of the lock owner, thereby delaying its completion and the release of the lock needed by the higher priority task. As depicted in Figure 2.2, this scenario leads to an unbounded priority inversion, which can ultimately cause system-wide failure. The situation was observed during the Mars Pathfinder mission, causing total system resets in the spacecraft that jeopardized the mission's success [72]. Fortunately, a wide range of suspension- and spin-based resource sharing protocols [20, 27, 32, 62, 63] have been proposed for hard real-time systems over the

Figure 2.2: Example of an unbounded priority inversion when a high priority task is blocked by a low priority task locking a shared resource, and that task is preempted by a medium priority one.

years. Among these protocols, the Multiprocessor Priority Ceiling Protocol (M-PCP or MPCP) [62] is a suspension-based protocol for partitioned fixed-priority scheduling, which prevents deadlocks and bounds priority inversion to the duration of the interval in which a resource holds the lock on a device, known as a critical section [68]. This is achieved by lifting the effective priority of tasks holding a lock on a resource above that of all other tasks in the system. As a result, tasks in a critical section cannot be preempted. Although quite simple to implement, a limitation of this protocol is that it does not support nested critical sections, since a deadlock could occur when two tasks simultaneously compete for two or more common resources.

### 2.1.3 Availability of Resources

In trusted computing, availability is often overlooked in favor of confidentiality, integrity, and other security properties. In fact, most trusted operating systems [5, 61, 82] delegate the scheduling of applications to the untrusted OS [45], as (1) moving the scheduling logic to the trusted domain would significantly increase the size and complexity of the TCB, and (2) they are often designed as companion OSes. For instance, the Completely Fair Scheduler (CFS) in Linux v6.14 [35] is approximately 13,700 lines of code. Although the aftermath of disrupting the availability of a system such as a personal computer or a phone is in most cases not dramatic, the conclusions are different when dealing with critical real-time systems, such as industrial plants, avionics, or modern cars [39]. In this project, our effort goes into ensuring the availability of resources needed by real-time tasks.

In other words, when a task needs to run, we must ensure that all the resources it requires are available, so that it can perform its operations properly and within delays. However, such guarantees cannot be provided if the very component that manages the allocation of resources on the system is completely untrusted, and, as such, at least a minimal subset of scheduling decisions has to be trusted to enforce policies.

### 2.1.4 Multi-Tenancy

Whether in our car, on the plane, in the substations that deliver power to our house, in medical devices such as pacemakers, or even in our washing machine, the vast majority of real-time systems that we encounter everyday are closed systems. A closed system is a system in which all software and hardware components are known and fixed a priori, and for which changes are not possible at runtime. This usually allows system designers to make assumptions about security, schedulability of resources, as well as other aspects of the development that will facilitate the design and implementation. However, this lack of flexibility can rapidly become a limitation, particularly in industrial contexts, where a customer could decide to use the system offered by company  ${\mathcal A}$  for controlling some aspect of their plant, while also needing at a later point in time the software solution of company  ${\mathcal B}$  for monitoring other on-site events, which the customer should be able to setup dynamically at runtime, without having to reconfigure the entire machine. Unfortunately, this ability to have a multi-tenant, open system is not free, as many assumptions that were possible in a closed system no longer hold.

### 2.2 Trusted Computing on Arm Platforms

Arm AArch64 processors employ varying levels of privileges, known as Exception Levels (EL) [11], similar to the concept of rings on x86 processors. These privilege levels range from the least privileged EL0, usually reserved to user-level applications, to the most privileged EL3, typically reserved for the boot loader and security monitor. They enforce a hierarchical, horizontal isolation, which can show insufficient to properly isolate software components at the same level of privilege.

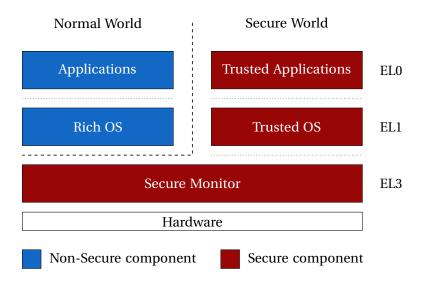

To address this issue, Arm A-profile processors enabled by the Security Extensions employ an additional isolation mechanism named TrustZone [15], which allows confidential computing on the Arm platform. More specifically, TrustZone allows system developers to partition platform resources (e.g., peripherals, memory) into two distinct regions commonly referred to as worlds, which are environments isolated from each other at the hardware level, following the access control matrix specified in Table 2.1. The TrustZone architecture, shown in Figure 2.3, introduces two worlds running alongside each other. The so-called secure world hosts the confidential environment and is used for security-sensitive operations. It comprises a trusted OS (TOS) with a minimal set of functionalities and trusted applications (TA). The secure OS is limited in the sense that it does not, for

Figure 2.3: Schematic architecture of a TrustZone-enabled system. The thick dashed line represents the worlds boundary. The thin dotted lines represent the in-world isolation between ELs. For simplicity, EL2 is not shown.

|                | Secure Region | Normal Region |

|----------------|---------------|---------------|

| Secure Context | ✓             | ✓             |

| Normal Context | Х             | ✓             |

Table 2.1: Access Control Matrix of the TrustZone architecture. When a CPU core is executing in secure mode, it has access to both secure and normal resources, whereas when executing in normal mode, it only has access to normal resources, i.e., access to secure resources is forbidden.

instance, implement device drivers or scheduling capabilities (passive OS) making it dependent on its feature-rich counterpart environment. The normal world, also referred to as non-secure world, hosts the untrusted, feature-rich part of the system, the so-called Rich Execution Environment (REE). The scheduling of TAs is initiated by client applications (CA) in the normal world when a sensitive service is requested. The switch from normal world to secure world is then performed via a conduit method, the smc (Secure Monitor Call) privileged instruction [16], which preempts execution and traps to the secure monitor (SM) that forwards the request to the TOS. This context switch is only performed on the core executing the smc instruction, and does not alter the state of the other processors on the platform, which can run in any of the two worlds independently. Should a scheduled TA require access to an external device (e.g., network card or hard drive), it will send a request back to the normal world – implementing the necessary drivers – which will execute the task on its behalf.

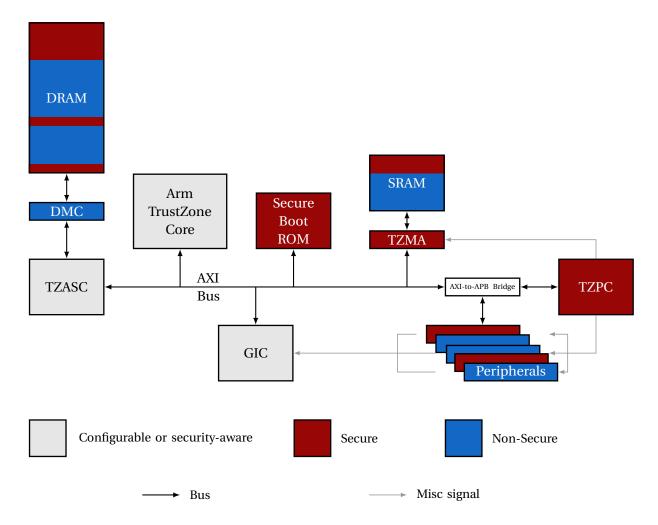

Figure 2.4: Simplified schematic architecture of the hardware components of a TrustZone-enabled system. For simplicity, only the components discussed in Section 2.2.1 are shown.

#### 2.2.1 Enforcement

Depending on the context of execution, i.e., normal or secure, the Non-Secure (NS) bit is set in the Secure Configuration Register (SCR). The SCR can only be modified in a privileged execution context, typically in secure EL3 when EL3 is implemented. As depicted in Figure 2.4, numerous hardware components are then used to enforce TrustZone's security mechanisms. For on-chip static memory, e.g., the SRAM or the ROM, the TrustZone Memory Adapter (TZMA) [8] is used to split the memory into a secure region, and a non-secure (or normal) region, with the location of the separation between the two being controlled by the R0SIZE input signal of the TZMA. For off-chip memory, the TrustZone Address Space Controller (TZASC) [7, 10] is placed on the bus between the CPU and the Dynamic Memory Controller (DMC) – which manages accesses to the main memory. It is responsible for dynamically partitioning the main memory, and enforcing access restrictions

based on the security status of the bus transaction, resulting from the NS bit, and that of the targeted memory region. In case access is not allowed, the ASC forbids it and signals the violation to the core attempting access via an asynchronous abort. The Generic Interrupt Controller (GIC) [12] is an external interrupt controller that is responsible for the configuration, prioritization, and routing of interrupts. It supports the TrustZone security extensions and allows interrupts to be configured as secure or non-secure. Interrupts configured as secure can only be delivered to the secure world, and any attempt to modify the configuration of a secure interrupt originating from the normal world will be prevented by the GIC. Finally, the TrustZone Protection Controller (TZPC) [8] offers an interface to dynamically configure peripherals as secure or non-secure [60]. The TZPC can also be used as an interface to configure the TZMA, by connecting its output signal TZPCR0SIZE to the R0SIZE signal of the TZMA.

#### 2.2.2 Limitations

TrustZone is an aging technology, it was first implemented in the ARM1176JZ(F)-S [8, 9] processor released in 2004. It is known to be vulnerable to privilege escalation attacks [24], fault injection attacks [73], as well as many other types of attacks [25]. Furthermore, its design and implementation model comes with a lot of limitations [40], such as a limited number of secure partitions (e.g., 8 for TZC-400 [7]), the large granularity of isolated partitions (32kB), the asynchronous aborts it generates on illegal accesses to the main memory, making e.g., the reconstruction of faulty instructions significantly harder than with a synchronous abort, and the fact that most TrustZone hardware components are neither standardized, nor mandatory (e.g., TZASC, and TZPC), limiting the portability of a design across different platforms. However, it is still the most commercially available trusted computing technology on Arm platforms to this day, compared to the very recent and more powerful Arm Confidential Compute Architecture (CCA) [14], which, to our knowledge, is not available on any testing board as of today.

### 2.3 Remote Attestation Model

A remote attestation protocol typically consists of at least two entities, each holding one or multiple roles in the attestation process, and which are often reduced to that of the Verifier and the Prover or Attester. The purpose of remote attestation is for a trusted Verifier to establish trust in an untrusted remote party, the Prover, that will need to prove it is running in a correct state in order to be trusted.

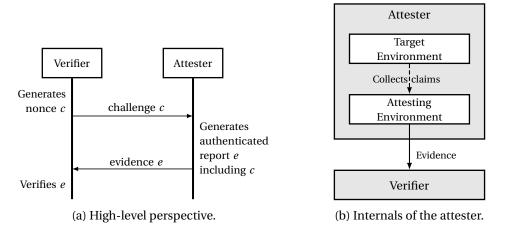

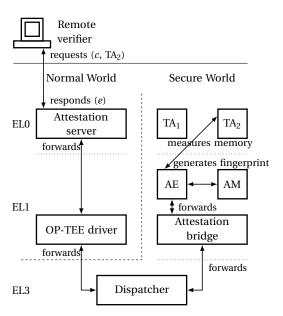

Following the glossary of the Trusted Computing Group (TCG) Attestation Framework Specification [77], and that of the Internet Engineering Task Force (IETF) Remote ATestation procedureS (RATS) Architecture [19], we refer to the Prover as Attester and elicit its structure, as shown in Figure 2.5b. The Attester and, more specifically, its Attesting Environment (AE) must perform measurements – individually called claims – of its components. Those claims are then packaged into

Figure 2.5: Remote attestation process between an attester and a verifier.

an evidence that it will sign and forward to the Verifier. This signature provides authentication of the AE and guarantees the integrity of the collected claims. The measured components are collectively described as the Target Environment (TE), of which the AE can be a part.

The remote attestation protocol is triggered via a challenge-response exchange between the Verifier and the Attester, which, as shown in Figure 2.5a, is typically initiated by the Verifier. Upon reception of the challenge, the AE will collect measurements of the TE. Such measurement usually consists of a cryptographic hash of immutable data, namely the program code and program data, due to the unpredictability of the state of mutable data such as program memory, and therefore only focuses on attesting launch-time integrity, leaving runtime integrity and other security properties (e.g., availability) out of the scope of the attestation process. The measurements are then aggregated into an evidence, signed with the received challenge for freshness, and sent to the Verifier as part of the response.

A fundamental requirement in remote attestation is that the AE must be trusted to perform measurements accurately. If the AE is compromised, the evidence it produces cannot be relied upon. In order to establish trust into the Attesting Environment, it is necessary to depend on a trusted entity that will be able to attest to its integrity as part of a so-called Chain of Trust (CoT). Each link or component of this chain is verified by the previous one, with the first element being the Root of Trust (RoT).

### 2.3.1 Root of Trust

Although the exact definition of a Root of Trust seems to be vendor-specific [6, 41, 78, 80], some characteristics are prevalent. From these characteristics, we define the RoT as an inherently trusted, preferably small, core security component of a device that offers the necessary set of critical features

to extend or establish trust in the underlying system. It provides functionalities such as trusted or measured boot, and storage of secret cryptographic keys. It is trusted to always operate in a dependable manner, as any alteration of its behavior will go undetected. It is often implemented as a hardware chip, commonly referred to as a TPM [79], which is impractical and too expensive for smaller systems such as IoT or Edge devices. For these platforms, the Trusted Computing Group (TCG) recommends other alternatives, one of which suits our needs: the Device Identifier Composition Engine (DICE) [75].

### 2.3.2 Device Identifier Composition Engine

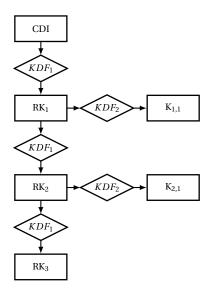

The DICE, standardized by TCG, is a capability of a Root of Trust with minimal requirements [76] which boil down to (1) secure storage of a Unique Device Secret (UDS), (2) measurement capabilities to measure the First Mutable Code (FMC), that is, the first software layer after the DICE, and (3) hashing capabilities to generate the private key for the FMC, based on its measurement and the UDS. In DICE terminology, such a private key is referred to as a Compound Device Identifier (CDI), and is used in place of the UDS for subsequent layers.

### **TCB Layering**

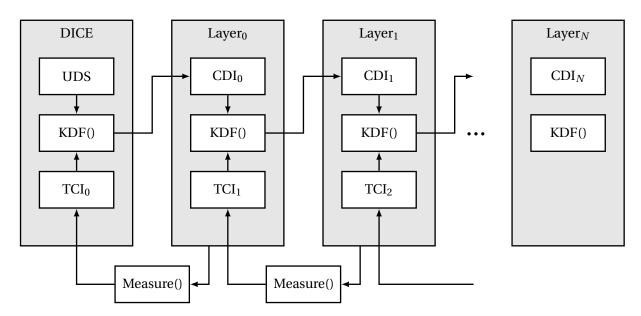

DICE has a layered architecture that follows the execution states entered progressively. Starting from a base hardware layer, each layer i+1 is measured and  $\mathrm{CDI}_{i+1}$  is derived from (1) that measurement, and (2) the  $\mathrm{CDI}_i$  of the layer performing the DICE flow. The measurement of a layer with optionally other identifying information, such as configuration variables, are collectively referred to as the TCB Component Identifier (TCI). The derivation of CDIs is performed using a one-way function, typically a cryptographically secure key derivation function (KDF).

Given a key derivation function  $KDF(ikm, salt) \mapsto okm$  with input key material ikm, salt salt, output key material okm, and implicit output length parameter, the CDI  $CDI_{i+1}$  of layer i+1 can be computed as follows:

$$CDI_{i+1} = KDF(CDI_i, TCI_{i+1})$$

Once the next TCB layer – here layer i+1 – has been constructed,  $\mathrm{CDI}_i$  is made unavailable (i.e., securely erased or protected) and control is passed to layer i+1, which receives its computed  $\mathrm{CDI}_{i+1}$  and, in turn, can execute this flow for the next boot stage, as depicted in Figure 2.6. It is important to note that CDIs can also be used as root keys for sealing or attestation purposes, with actual secret keys being derived from them for domain separation. Similar to the Program Configuration Register (PCR) in a TPM, the layering of CDIs allows the detection of modifications in previous layers, therefore binding the execution of layer i to the integrity of its TCI and that of all previous layers, creating a Chain of Trust (CoT).

Figure 2.6: TCB layering in the DICE architecture. Each layer i measures the next one (i+1) and get the result as  $TCI_{i+1}$ , which it uses as input with its own  $CDI_i$  to derive the next private  $CDI_{i+1}$  key, via the key derivation function KDF(). The first layer, that is, the DICE RoT, uses the Unique Device Secret (UDS) as CDI.

## **Chapter 3**

## **Motivation and Goals**

In this work, the aim is to provide attestable availability guarantees to tasks deemed security sensitive, specifically in the context of industrial OT systems. For that purpose, our design should be implementable on readily-available hardware, and as such should not rely on any kind of hardware modification. Consequently, our goal is also to identify the set of hardware components necessary to our design. We also highlight that, for different reasons such as Intellectual Property (IP), providers of industrial solutions often seek to keep their code and runtime data confidential from other actors present on the system.

Given the widespread adoption of TrustZone on Commodity Off-the-Shelf (COTS) Arm A-profile processors, it is currently the technology of choice for designing and implementing industrial systems on an Arm platform, while supporting certain guarantees of trust. We also investigate the use of other major Instruction Set Architectures (ISA) for the implementation of our design, such as RISC-V, and discuss our findings in Section 7.1. Due to their commercial availability, versatility, power efficiency, and general efficiency [48, 65], we conclude that, to this day, Arm platforms are better suited to the requirements of this work.

### 3.1 Problem Statement

Building on the above discussion, we define below the objectives for the system that we design.

$G_1$ : Guaranteed attestable availability. Our primary objective is to provide critical tasks with guaranteed, deterministic, and timely access to the computational and non-computational resources they require. Furthermore, we want remote entities such as Supervisory Control And Data Acquisi-

tion (SCADA)<sup>1</sup> systems to be able to verify that the deployed real-time control loops are scheduled and executed following a predefined set of rules, which collectively compose the policies of real-time tasks.

**G<sub>2</sub>: Confidentiality and attestable integrity.** Following IP and correctness requirements, code and data of critical tasks should be kept confidential from software running in the non-secure world. Simply put, the real-time tasks should be able to be loaded and run in total isolation from the untrusted subsystem. Similarly to  $G_1$ , we want a remote entity to be able to verify the integrity of the critical tasks loaded on the system.

**G<sub>3</sub>: Separation of powers.** We do not wish for an omnipotent monitor that would be blindly trusted to craft policies, enforce them, and report their correct enforcement. Instead, we want applications to submit their own policy to the Monitor, while being supervised by a third party verifying that it correctly enforces the said policies.

**G<sub>4</sub>: COTS hardware.** Our design shall not resort to hardware modification, but instead should build on top of existing hardware primitives available on COTS platforms.

$G_5$ : Open, multi-tenant system. We make it a goal to design a system that supports multiple mutually distrusting tenants, each able to run their own critical and non-critical applications that can be launched dynamically at runtime, without compromising the objectives set beforehand.

$G_6$ : Multicore usage. Safety-critical systems increasingly require sufficient compute power [66], and uniprocessor platforms may quickly reach their limits in real-time, open systems. By exploiting all available cores, the system can achieve better responsiveness, and execute comparatively more tasks at any given time.

### 3.2 Threat Model

We trust the hardware of the platform, and that of all external peripherals to be bug-free and work according to their specification. Once their integrity has been verified, we also trust all privileged (EL3 to EL1) software running in the secure world. We consider the established threat model in [50], in which it is assumed that any software outside the TCB is controlled by a powerful attacker. This includes all userland applications, including the real-time tasks but, as our design will show, not

$<sup>^{1}</sup>$ A SCADA is a supervisory system that can collect data from, and monitor the individual hard real-time systems in a plant.

their policy, as well as the privileged, untrusted kernel. Side-channels and physical attacks are considered outside the scope of this work. In this context, an attacker would, for instance, be able to:

- Run arbitrary computation, potentially privileged, on the system,

- · Intercept and tamper with the manifest provided by an application upon loading,

- · Try and launch fake critical tasks with malicious policies and maximized utilization,

- Try and lock shared resources without ever releasing them,

- Try and compromise the integrity of peripherals, e.g., by exploiting the Dynamic Voltage and Frequency Scaling (DVFS) [73, 86], causing data corruption and faulty computations, or

- Try and shutdown cores or the entire system.

### 3.3 Closely Related Work

For the past two decades, there has been an increasing interest in enabling Trusted Execution Environments with availability guarantees, which has led to the publication of multiple works [4, 51, 64, 84–86, 89] sharing a more or less large subset of our goals. We present here a few of these works that serve as the foundation of our study, and provide a more complete discussion in Chapter 8.

Mr-TEE [85] is a Trusted Execution Environment (TEE) that leverages TrustZone to provide safetycritical tasks with availability guarantees. It introduces a novel approach to share devices between the secure and non-secure worlds, but does not benefit from a mechanism to prove scheduling or execution of the tasks. Furthermore, its secure scheduler only runs on a single core, which, while offloading complexity from the TCB, could rapidly become a limitation in some industrial contexts where the period of critical tasks can be as low as 1ms. Aion [4] is a security architecture delivering new hardware primitives that guarantee remotely attestable progress and device access to real-time tasks, which are executed in trusted enclaves inside an open system. Aion brings hardware extensions to the Sancus [55] architecture, which is itself a hardware extension of the MSP430 architecture, contradicting our goal  $G_4$ . Hora [89] is a subsequent work providing similar security guarantees while also preventing untrusted applications from compromising the drivers of shared peripherals. It conflicts with goal  $G_4$  due to its reliance on hardware modifications, but leverages the available multicore platform, aligning with objective  $G_6$ . RT-TEE [86] is a Real-Time Trusted Execution Environment, complementary to Aion and Hora, aiming to bring availability guarantees to real-time tasks of Cyber-Physical Systems (CPS), with careful considerations for the size and complexity of the TCB. RT-TEE targets COTS embedded platforms, which are generally closed, single-tenant systems, which conflicts with our goal  $G_5$ , and only feature a single core due to space, weight, and power (SWaP) restrictions, diverging from  $G_6$ . PEARTS [54] introduces a real-time proof of execution architecture, enabling a remote verifier to check the integrity and availability needs of

|                                          | W. W.      | Aloy<br>OV | A. TER  | 2020       | PEARS        | Beho | to man o |

|------------------------------------------|------------|------------|---------|------------|--------------|------|----------|

| Guaranteed Attestable Availability       | •          | •          | •       | •          | •            | 0    | •        |

| Confidentiality and Attestable Integrity | •          | •          | •       | •          | lacktriangle | •    | •        |

| Separation of Powers                     | $\bigcirc$ | $\bigcirc$ | $\circ$ | $\bigcirc$ | $lackbox{}$  | •    | •        |

| COTS Hardware                            | •          | $\circ$    | •       | $\bigcirc$ | •            | •    | •        |

| Open, Multi-Tenant System                | •          | •          | $\circ$ | $\circ$    | $\circ$      | •    | •        |

| Multiprocessor Usage                     | $\circ$    | $\circ$    | $\circ$ | •          | $\circ$      | •    | •        |

Table 3.1: Comparison of our envisioned design with earlier works, with regard to our goals.  $\bullet$  means a goal is part of the design,  $\bigcirc$  means it is not, and  $\bullet$  means a goal is only partially implemented. For instance,  $\bullet$  for  $G_1$  here either means that availability guarantees are provided, but are not verifiable, or that availability can be attested but is not guaranteed through trusted scheduling.

real-time applications executing in the normal world. It is aimed at closed, low-end, single-core IoT devices, and leverages the TrustZone architecture to host its attesting environment. It runs real-time tasks in the normal world, and does not provide any guarantees of confidentiality. The idea behind objective  $G_3$  comes from the work of C. Castes, et al. [22] in which they reflect on the monopoly of powers exercised by trusted software, and propose an alternative architecture within which the so-called powers of (1) emitting policies, (2) enforcing policies, and (3) attestation are all split across different components of the system. To summarize, Table 3.1 displays an overview of how the design of the closely related works mentioned above compares to the goals of this work.

## **Chapter 4**

# Design

In this section, we discuss the design choices of our system. We first elaborate on the elements required to bootstrap it, and follow with the description of its components, which we organize into three main categories.

### 4.1 System Requirements

Based on the requirements for DICE implementation (see Section 2.3.2) and the technologies offered by the TrustZone security extensions (see Section 2.2.1), we elicit the minimal set of hardware requirements to provide our system with the usability and security guarantees that we derived in Section 3.1.

### 4.1.1 Hardware Components

To implement DICE, a secure mechanism for storing the Unique Device Secret (UDS) is required, as specified in [38]. To ensure availability, TrustZone hardware components, such as the Protection Controller, Address Space Controller, and a TrustZone-aware GIC, are leveraged to enforce isolation. These components allow us to restrict peripheral and interrupt access to the secure world, assign the memory of critical tasks to the secure world, and enforce access control policies on system bus transactions.

In order to bootstrap the availability of compute resources, we need a mechanism to dependably retrieve control over the system, so that new scheduling decisions can be taken when required. This necessitates a timer device, immutable from the non-secure subsystem, which triggers at configured intervals of time and traps to the secure environment. This type of timer can be available

in two ways on Arm platforms: (1) as a processor timer, that is, the EL1 secure physical timer (CNTPS\_EL1) [13], or (2) as an external SoC timer configurable as a secure device, that is, in the presence of a TrustZone-enabled GIC and memory controller.

We survey about 30 Cortex A-profile multicore boards in order to identify evaluation kits that suit our needs, and report our findings in Appendix A for 19 of them, for which we could find sufficient relevant documentation. Among those 19 boards, we find that 13 of them have the necessary requirements.

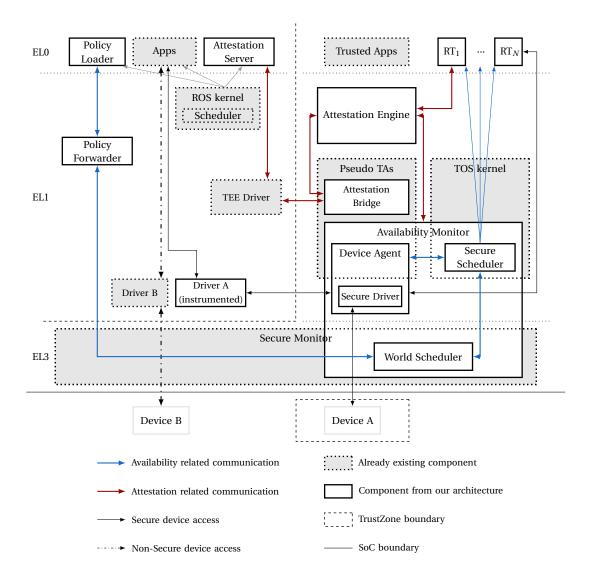

### 4.2 The Three Powers

In order to decouple the power to put law into action, make the law, and judge the law, we split our design into three main entities, following the political model of separation of powers [26]. Similar to [22], we make an analogy between these three powers and the three concepts of enforcement, policy enactment, and attestation, respectively. Not only does this separation allow users to avoid having to blindly trust a single omnipotent entity, it also allows one to reason more clearly about our design and how to provide and verify availability guarantees that comply with the requirements provided by users. We show an overview of the architecture of our design in Figure 4.1, and discuss its different components in the following sections.

### 4.2.1 Executive: the Availability Monitor

In order to provide availability guarantees to real-time tasks, we must ensure the enforcement of the policies of those tasks. To fulfill that function, we propose an availability monitor (AM), whose role is to schedule critical tasks according to their attached policy, and provide them access to required computational and peripheral resources in a timely manner. The AM is designed as a composite entity, with components working hand in hand to provide the required properties. Similar to [86], we design a two-layer hierarchical scheduler [31] which comprises a world scheduler at the top layer, and sub-schedulers for each world at the bottom layer: the secure scheduler and the normal-world scheduler. Although the world and secure scheduler can be thought of as the head of the AM, they are not omnipotent as they mainly focus on sharing computational resources, and delegate management of external resources to Device Agents (DA) <sup>1</sup>. The DAs, commanded by the secure scheduler, focus on enforcing temporal and spatial isolation of shared resources to ensure their availability to critical tasks.

<sup>&</sup>lt;sup>1</sup>In multiprocessor resource sharing protocols, particularly in the context of the Distributed Priority Ceiling Protocol (D-PCP) [63], Resource Agents was the name given to special tasks that handled access to resources on behalf of requesting tasks. We reuse the name of agent in that context.

Figure 4.1: Overview of the architecture of our design. For simplicity, communication of the normal world scheduling trusted applications (TAs) have been omitted. Note that all communication between the normal and secure world has to go through the secure monitor in EL3; for simplicity, we omitted that additional hop.

#### The World Scheduler

The world scheduler is a preemptive scheduler that will preempt execution of the current world to resume one or the other, based on the requirements elicited in policies. It is responsible for enforcing budget constraints on the sub-schedulers, and is agnostic to the actual scheduling algorithm they implement. It executes at the highest level of privileges on the platform, and as such, its set of functionalities should be kept as small as possible to reduce its attack surface and allow for formal verification. In an industrial context, it is crucial that critical tasks – which need to execute in the secure world to benefit from the guarantees our design provides – complete before reaching their deadline, even at the risk of starving the normal world. For that reason, we give the secure scheduler an infinite budget and only retrieve control when it encounters idle time. Given this constraint, we consider the NS scheduler as an aperiodic task and envision a background scheduling algorithm to handle such tasks (see Section 2.1.1), which means that the NS scheduler will only be scheduled when its secure counterpart is not busy. This method presents the advantage of having no impact on the schedulability of critical tasks, at the risk of starving the normal world. Background scheduling also makes it easier to reason about the schedulability of critical tasks, while facilitating the implementation of the world scheduler, therefore reducing the complexity of the TCB.

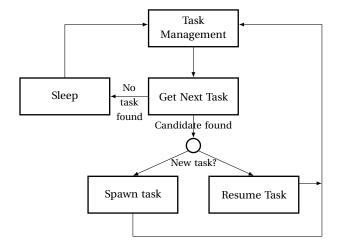

#### The Secure Scheduler

The secure scheduler is the section of the AM that is responsible for enforcing availability guarantees of computational resources to critical tasks. It leverages a partitioned, priority-based, event-driven, preemptive, fixed-priority scheduling design. Since safety-critical systems increasingly depend on multicore for sufficient compute power [66], we design our scheduler to take full advantage of all application processors on the platform, but take a partitioned scheduling approach. This means that each task remains assigned to the same core for its entire lifetime; this assignment is sometimes referred to as the affinity of the task. Compared to global scheduling, partitioned scheduling has the advantage of being less complicated to implement, helping towards our goal of keeping a small TCB, as it does not require complex load-balancing algorithms, and many techniques used in uniprocessor scheduling can be applied or easily adapted to it. Moreover, it does not suffer from the performance overhead of migrating tasks across cores [32], which can increase the scheduling latency. Until a first task gets scheduled on any given core, the secure scheduler responsible for that core acts as a polling server, periodically checking if it has received a critical task from another core, and suspending itself until the next polling tick if it has not. When a first task is received, the polling mechanism in which ticks occur at regular intervals switches to an event-based approach, in which the scheduler is configured to tick on the next event, which has a relative upper bound equal to the execution time of the job, defined in the provisioned task policy. In this case, the next event refers to the suspension of the current task leading to the scheduler retrieving control over the core, which can occur either because the task has completed, or because of its preemption by a higher priority task, or because it has blocked on a shared resource. At every tick, the scheduler takes a

new scheduling decision, which consists in (1) retrieving the highest priority task in its pool of ready tasks, and (2) retrieving the next nearest release of a job. The next task is then scheduled on the core, and the next scheduling event is configured to be the earlier between the end of the execution of the current task, and the next release. The configuration of the next tick allows the scheduler to impose an upper bound time limit after which it will retrieve control over the core, so that it can take a new scheduling decision. This mechanism is realized through the use of a core-private secure timer. This timer is configured such that it can only be programmed from, and can generate interrupts routed only to, a privileged secure context (i.e., S-EL1 or higher). Furthermore, its interrupts are assigned the highest possible priority on the platform, above all others, thereby taking precedence over any concurrent interrupts. In the case where no task is ready to be scheduled on the core, we say that the scheduler becomes idle. When the scheduler encounters idle time, it is able to suspend itself and gets preempted by the world scheduler.

To share or not to share. Depending on the total utilization of a core by the set of critical tasks it has been assigned, as well as the requirements of the end-customer, it might either be interesting or too demanding to share the core between the secure and non-secure worlds. If the secure scheduler does not release the core while idle, it puts the core into a low-power state until it is awakened by the next scheduler tick. On the other hand, when the core is shared between the two worlds and returned by the trusted scheduler, a context switch will occur when the secure scheduler becomes idle. This switch, operated by the world scheduler, comes at a certain cost that we measure in Section 6.1. While the penalty incurred by such an operation is acceptable when returning control to the normal world, as it does not host applications with a hard deadline, this performance overhead might become problematic when a critical task needs to be scheduled. Especially in the cumbersome case where the next secure scheduling event would happen during the transition from the secure world to the non-secure world. For that reason, we leave the option to the system designer to choose whether or not to allow sharing of a core between the two worlds.

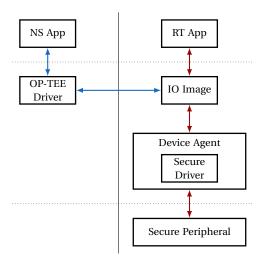

### The Device Agents

The secure scheduler interacts with entities that we refer to as Device Agents (DA), which are responsible for enforcing strict spatial and temporal isolation on the peripheral they manage, collectively ensuring the availability of shared resources on the platform. DAs act as wrappers around secure drivers, and provide a firewall-protected interface to the configuration and functionality of the device they protect by monitoring every access.

**Spatial isolation.** Spatial isolation is a necessary component for bootstrapping availability on the system, as it enforces strict access control to preserve the device logical and physical integrity. When initializing, DAs leverage the security extensions available on the platform to isolate their device

from the untrusted NS world, and enforce access control at the bus level. Generally, a program can communicate with a peripheral in three main ways: (1) via Memory-Mapped IO (MMIO), that is, the device memory is mapped to the address space of the system by configuration of the page tables in the memory management unit (MMU), (2) via interrupts, generated by the peripheral and routed to a core, where interrupts are enabled by configuring the GIC and the peripheral through MMIO, and (3) via Direct Memory Access (DMA), where the device bypasses the CPU and directly reads from or writes to the main memory, at addresses configured by the driver through MMIO. Mapping a device to the secure world thus consists in isolating its memory-mapped registers, isolating the interrupts it generates, and in the case of DMA devices, configuring the device as secure so that it is granted read and write access to secure memory. Once secure devices are properly isolated, the DAs are able to monitor every MMIO access coming from the normal world and secure applications, as it is the only available interface at their disposal. The availability of a peripheral can be disrupted by supplying malicious values to control registers, targeting two main attack vectors [86]: either its logical integrity (e.g., changing the detection thresholds of a proximity sensor) or physical integrity (e.g., by over-raising the frequency of a core [73]), causing the peripheral to act unexpectedly. A Device Agent can prevent such behaviors by first filtering requests, that is, by allowing or disallowing based on the permissions of the requester; and second by sanitizing the content of the requests, e.g., by verifying the configuration values are within the operational bounds of the device. Finally, a remaining trivial attack that a fully compromised normal world OS could perform would be to simply shut down the system. In order to prevent such an attack, as well as more elaborate ones targeting, for instance, the Device Voltage and Frequency Scaling (DVFS) [73, 86], we can firewall the power management functionality of the SoC behind a dedicated Device Agent.

**Temporal isolation.** In general, a real-time system comprises multiple tasks, all of which may require access to different resources. In an ideal world, every task requires a different set of peripherals, which would make scheduling of resources straightforward. However, the reality is quite different, and tasks running in parallel (e.g., with intertwined scheduling of jobs on a single core, or at the same time on different cores) can compete for the same devices, leading to contention issues. To mitigate these issues and handle the sharing of resources on the system, we use a suspension-based Multiprocessor Priority Ceiling Protocol (MPCP) (see Section 2.1.2), and consider all SoC-external resources to be global resources; that is, all external resources can be acquired by tasks running on any core, provided the required resources are declared in their policy. The MPCP protocol imposes an upper bound limit on priority inversions, equal to the access time of the critical section of the lower priority task [27, 62]. Device Agents further constrain this bound to the provisioned execution time of the owning task, as specified in its task policy, after which it is forced to return the device to the Availability Monitor. It is therefore the responsibility of the policy provider to ensure that the parameters specified for a task  $T_1$ , potentially blocking a higher priority task  $T_2$ , are carefully chosen so that the blocking time induced on task  $T_2$  does not prevent it from completing before its deadline.

When a change of ownership is observed, the DAs ensure their peripheral is reset to a neutral

state. This mechanism prevents (1) the leakage of potentially private information to the normal world or between mutually distrusting real-time tasks, and (2) corrupted behavior resulting from a critical task that expects the peripheral to be in a given state while it is not.

**Peripheral sharing across worlds.** At design time, depending on the requirements of critical-tasks, a set of peripherals can be mapped to the secure environment. In order to provide availability guarantees to real-time tasks by applying temporal and spatial isolation of required devices, it is mandatory that all peripherals that may be claimed by critical tasks are assigned to the secure world. From this point on, each individual device can either be shared across both worlds, or exclusively owned by the secure world. A device is exclusively owned by the secure world if and only if the normal world has no way of accessing it, no matter the level of privilege (EL2, EL1, or ELO) it is executing at. This access control policy is enforced by TrustZone and configured by the AM. While exclusively secure devices present advantages in terms of simplicity of design and security, as no interaction is possible from outside of the TCB; it prevents normal world applications from legitimately using them. In order to share devices, we use a split-driver model [64, 84–86] in which the drivers of such peripherals present a normal and a secure split. The normal split exposes the feature-rich application-facing part of the driver, while the secure split exposes the low-level peripheral-facing part, directly communicating with devices. When a normal world application wants to use a peripheral, it calls an interface exposed by the NS driver, which will need to invoke the DA of that peripheral in order to interact with it.

**Interrupt management.** An important aspect to consider when handling real-time tasks with strict timing requirements is the case of interrupts. In order to perform a Denial of Service attack on the Availability Monitor, a malicious untrusted OS could configure a non-secure peripheral such that it continuously triggers interrupts. The interrupts handled by the trusted OS and those that are not are treated by the GIC as two different kinds of interrupt [82]. When executing, our TEE masks the interrupts that it did not configure, and unmasks them when returning control to the normal world, thereby mitigating such an attack vector. Although non-secure interrupts are handled by our design since they are outside the TCB and constitute an important attack vector, we allow greater flexibility in how secure interrupts are implemented. Since (1) the set of secure peripherals (and therefore their driver with DA) is chosen at design time, and (2) the access control policy and actual implementation of specific Device Agents depend on the requirements of the end-customer, we let the system designer carefully decide how interrupts are handled and shared in the secure world. Furthermore, our design currently does not support sharing interrupts from secure devices to normal world observers. We refer to the state-of-the-art [85] for such a mechanism. In order to share secure interrupts to the normal world, [85] creates a communication channel between the S and NS drivers, which they refer to as Shared Secure Peripherals Notifier (SSP Notifier) which has a normal world Notifier on one end, and a secure world Notifier on the other end. When a secure device raises an interrupt, it is handled by the S driver, which in turn triggers a normal world interrupt via the

secure world Notifier, to which the normal world Notifier is subscribed, and can then forward to the normal world driver for further handling.

### 4.2.2 Legislative: Real-Time Policies

In the previous section, we discussed how the Availability Monitor can enforce the availability of computational and non-computational resources to real-time tasks with a hard deadline, following strict requirements elicited in the so-called task policies. We now discuss these real-time tasks with their task policies, and how to securely provision them to the AM. Note that, except for availability, secure aperiodic tasks also benefit from all the security guarantees discussed below.

### **Secure Applications**

Following the goals elicited in Section 3.1, the requirements for critical applications boil down to ensuring and attesting their integrity, preserving their confidentiality, and providing them with availability guarantees. As discussed previously, once loaded with their attached policy, availability is enforced by the Availability Monitor. With regard to secure applications (not their policy), this leaves open three questions: (1) How to provide confidentiality at rest and in use? (2) How to ensure actual loading? and (3) How to ensure and prove their integrity?

**Confidentiality.** Confidentiality in use is warranted by the TrustZone part of our system. Once loaded in the Trusted Execution Environment (TEE), tasks execute in complete isolation from any software in the normal world, regardless of its level of privilege. Moreover, since secure tasks distrust each other, we leverage the MMU to configure userland page tables and isolate their respective address space, ensuring the confidentiality of their program code, data, and memory. Regarding confidentiality at rest, confidentiality of task binaries is achieved through the use of cryptography. Our TEE should support the loading of encrypted binaries, which it shall decrypt inside the secure world so that no untrusted actor on the system can access the IP code.

**Guaranteed loading.** Generally, the binaries of secure applications are stored on the disk and retrieved by the Trusted OS (TOS) when loading them [82]. Since porting device drivers to the secure world increases the size and complexity of the TCB, TOSes generally ask their counterpart feature-rich OS to perform actions on their behalf. Examples of such mechanisms are reading from, and writing to the disk. In order to perform disk operations, a TOS issues a request in the form of a Remote Procedure Call (RPC) to the untrusted OS that implements a file system as well as necessary disk drivers. The normal world OS then performs the read or write operation and returns from the RPC. When we consider all untrusted software to be under the control of an attacker (see Section 3.2), this mechanism can break all availability guarantees (e.g., CVE-2025-46733). For

instance, a malicious kernel could simply deny requests to the file system, preventing the TOS from loading secure applications. In order to remediate that issue, our design should support the pre-loading of critical tasks. Pre-loaded tasks are appended to the TOS image and are thus loaded at the same time as the trusted kernel. They are then stored in secure, read-only memory and can be loaded without the intervention of the non-secure OS.

**Integrity.** The integrity of trusted tasks can first be verified in two ways, depending on whether the task was pre-loaded or fetched from the disk. In the former case, the task binary is part of the trusted kernel image, whose integrity is checked by the Root of Trust at boot time, prior to being run. As the binary is then stored in trusted read-only memory, its integrity is preserved and does not need to be asserted again when mapped into memory. When the trusted task is fetched from the disk, we are again faced with two different cases, depending on whether or not the end-user decided to encrypt the binary for confidentiality at rest. Should it be the case, our TEE shall support authenticated encryption schemes to securely store binaries, such as AES in GCM mode [33]. Authenticated Encryption is an encryption scheme that provides confidentiality while ensuring integrity of the data. Finally, if the binary is not protected for confidentiality, but still requires authentication, its policy should include a field specifying the checksum of the task binary.

### **Task Policy**

Task policies are the set of properties and requirements that define critical real-time tasks. They specify the parameters of real-time tasks as defined in Section 2.1.1, which are their period, execution time, core affinity, and set of required shared resources, as well as a unique identifier binding them to a unique task (i.e., binary of a Trusted Application), and an explicit priority field. An example of such a policy is displayed in Listing 4.1. The task policies are user-provided with the help of an unprivileged *policy loader* in the normal world (i.e., NS-EL0). The *policy loader* then sends a request to the privileged *policy forwarder*, which forwards the policy to the world scheduler, subsequently passing it onto the secure scheduler. This exchange is depicted in Figure 4.1. Collectively, task policies form the scheduling policy of the system, making them a central part of the availability guarantees and a potential attack vector. For this reason, they should be authenticated. Authentication is used to verify that the policy has not been tampered with, and that it was defined by an authorized entity.

**Integrity protection.** A malicious entity in the non-secure world could try to modify the properties defined in a task policy that is being forwarded to the secure world. We add a mandatory key field in polices that holds a cryptographic hash of the values defined in that policy. The cryptographic scheme used to hash the policy must provide preimage resistance, second preimage resistance, and collision resistance, so that it is not possible for an attacker to alter the policy without altering the computed hash too.

**Authorized policies.** By simply hashing the policy, it would be trivial for an attacker to craft a malicious policy, or tamper with an existing one, and compute a new valid hash. We use a cryptographically secure signature scheme to circumvent this issue. In public key cryptography, a signature scheme allows an entity to sign a payload with a key only known to them; this key is referred to as the secret key. The signature is then sent alongside the payload, and can be verified by a third party with the public key of the signer. With this mechanism, it is possible for our TEE to verify not only the integrity of a policy, but also to ensure that it was created by an authorized entity. The storage of the secret key and the signing of the policies should be done in a secure environment and never on the system, as a malicious entity could record the secret key being used and later craft their own policies.

**Replaying the policies.** A malicious entity could record a valid policy and try to replay it multiple times in order to flood the secure scheduler and disrupt the system. Our design handles that case and does not authorize more than one instance of the same critical task at a time. Another attack could consist of an entity recording a maximum amount of valid policies to attain the same result as the last attack. We argue that it is the responsibility of the end-user to ensure that only the critical tasks required by a system exist on the said system, restricting the number of scheduled real-time tasks to the intended count.

**Rollback protection.** Currently, our design does not support rollback protection for the policies. However, we argue that such an attack vector can be detected by a remote verifier leveraging our Attestation Engine.

**Denied forwarding.** Finally, a corrupted *policy forwarder* could simply drop the policies instead of forwarding them. To mitigate that issue, our TEE should be able to support pre-loaded scheduling policies, similarly to the pre-loaded secure applications.

Listing 4.1: Example of a task policy.

### 4.2.3 Judiciary: the Attestation Engine

In this section, we discuss the design of our Attestation Engine (AE) for availability guarantees. Its purpose lies in ensuring that the Availability Monitor performs its duty in accordance with the received policies. In other words, the AE must be able to verify and show to a remote party a proof of unaltered execution for a target real-time task. [54] introduces and formalizes the requirements for this new security goal, which they refer to as Real-Time Proof of eXecution (RT-PoX).

#### **The Trust Anchor**

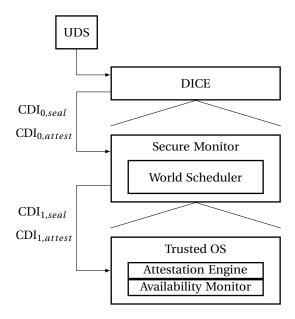

We use a Device Identifier Composition Engine (DICE) Root of Trust (RoT) to act as the trust anchor of our Attestation Engine. We leverage the layering architecture of DICE to extend the Chain of Trust up to the TOS, and generate two private keys (so-called CDIs) that are bound to both the hardware and software state of the device. One advantage of such a design is that, apart from a unique hardware secret, all private keys are generated at runtime and do not need to be stored on the disk. Among the two previously generated keys, the sealing CDI is used for sealing purposes and will serve as a root key for (1) decrypting the binaries of encrypted critical tasks, and (2) encryption and decryption for secure storage functionality in TAs. The other key, called the attestation CDI, will be used as a seed to derive a pair of cryptographic keys that will later be used by the Attestation Environment (AE) to sign evidence.

**DICE in more detail.** Starting from a hardware-stored unique device key, called in DICE [75] terms a Unique Device Secret (UDS), our design derives a new secret key (CDI) for each booting layer. Each layer constructs the key for the next one and destroys its own CDI before passing control forward. As described in Section 2.3.2, a layer derives the CDI for the next booting stage from its own CDI and a measurement of that stage, along with its configuration parameters, which together form the TCB Component Identifier (TCI). This layering architecture presents the advantage of producing keys that are not only bound to a unique device, but also to the state of the software running on the platform. Any incorrect state in the TOS or prior boot stages will produce different keys, ultimately resulting in an inconsistent attestation signature that can be detected by a remote verifier. As depicted in Figure 4.2, this Chain of Trust extends in the secure world up to the TOS, which can now be relied upon to execute attestation.

**Key rotation in the TOS.** In our design, the TOS needs to use private keys for multiple purposes, such as TA decryption, secure storage, and attestation. As private keys should only be used for a single purpose and a single cryptographic algorithm, we use a Key Derivation Function (KDF) to generate new keys from the CDI and obtain domain separation. However, as the TOS might need to probe the CDIs multiple times, we cannot simply erase them from memory once they have been

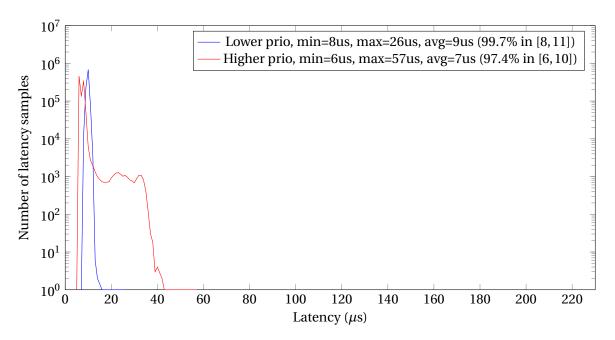

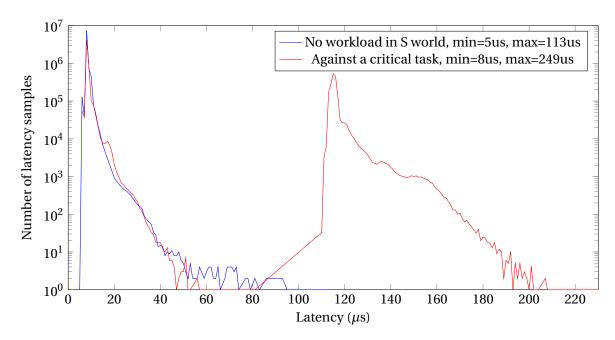

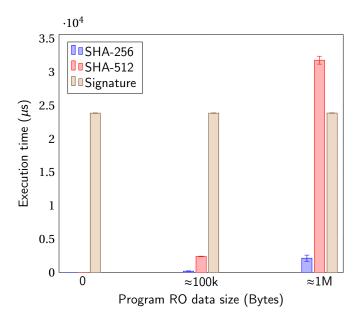

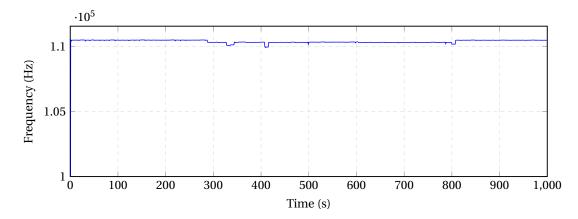

Figure 4.2: Illustration of the DICE layering in the secure environment of our architecture. Each layer measures the next one and produces CDI keys based on this measurement, its own CDIs, and optionally configuration parameters of the next layer.